Brigham Young University BYU ScholarsArchive

All Theses and Dissertations

2009-07-01

# Finding Alternatives to the Hard Disk Drive for Virtual Memory

Bruce Albert Embry Brigham Young University - Provo

Follow this and additional works at: https://scholarsarchive.byu.edu/etd Part of the <u>Computer Sciences Commons</u>

#### BYU ScholarsArchive Citation

Embry, Bruce Albert, "Finding Alternatives to the Hard Disk Drive for Virtual Memory" (2009). *All Theses and Dissertations*. 1727. https://scholarsarchive.byu.edu/etd/1727

This Thesis is brought to you for free and open access by BYU ScholarsArchive. It has been accepted for inclusion in All Theses and Dissertations by an authorized administrator of BYU ScholarsArchive. For more information, please contact scholarsarchive@byu.edu, ellen\_amatangelo@byu.edu.

### FINDING ALTERNATIVES TO THE HARD DISK DRIVE

### FOR VIRTUAL MEMORY

by

Bruce A. Embry

A thesis submitted to the faculty of

Brigham Young University

In partial fulfillment of the requirements for the degree of

Master of Science

School of Technology

Brigham Young University

August 2009

### BRIGHAM YOUNG UNIVERSITY

### GRADUATE COMMITTEE APPROVAL

Of a thesis submitted by

Bruce A. Embry

This thesis has been read by each member of the following graduate committee and by majority vote has been found to be satisfactory.

Date

Barry M. Lunt, Chair

Date

C. Richard G. Helps, Member

Date

Michael G. Bailey, Member

### BRIGHAM YOUNG UNIVERSITY

As chair of the candidate's graduate committee, I have read the thesis of Bruce A. Embry in its final form and have found that (1) its format, citations, and bibliographical style are consistent and acceptable and fulfill university and department style requirements; (2) its illustrative materials including figures, tables, and charts are in place; and (3) the final manuscript is satisfactory to the graduate committee and is ready for submission to the university library.

Date

Barry M. Lunt Chair, Graduate Committee

Accepted for the Department

Val D. Hawks Director, School of Technology

Accepted for the College

Alan R. Parkinson Dean, Ira A. Fulton College of Engineering and Technology

#### ABSTRACT

## FINDING ALTERNATIVES TO THE HARD DISK DRIVE FOR VIRTUAL MEMORY

Bruce A. Embry School of Technology Master of Science

Current computer systems fill the demand of operating systems and applications for ever greater amounts of random access memory by paging the least recently used data to the hard disk drive. This paging process is called "virtual memory," to indicate that the hard disk drive is used to create the illusion that the computer has more random access memory than it actually has. Unfortunately, the fastest hard disk drives are over five orders of magnitude slower than the DRAM they are emulating. When the demand for memory increases to the point that processes are being continually saved to disk and then retrieved again, a process called "thrashing" occurs, and the performance of the entire computer system plummets. This thesis sought to find alternatives for home and small business computer users to the hard disk drive for virtual memory which would not suffer from the same long delays. Virtual memory is especially important for older computers, which often are limited by their motherboards, their processors and their

power supplies to a relatively small amount of random access memory. Thus, this thesis was focused on improving the performance of older computers by replacing the hard disk drive with faster technologies for the virtual memory. Of the different technologies considered, flash memory was selected because of its low power requirements, its ready availability, its relatively low cost and its significantly faster random access times. Two devices were evaluated on a system with a 512MB of RAM, a Pentium 4 processor and a SATA hard disk drive. Theoretical models and a simulator were developed, and physical performance measurements were taken. Flash memory was not shown to be significantly faster than the hard disk drive in virtual memory applications.

#### ACKNOWLEDGMENTS

I wish to thank Dr. Barry Lunt for his insightful critiques of this thesis, along with his friendship and encouragement.

Professor Richard Helps is acknowledged for his ever vigilant devil's advocacy which sharpened my own thinking.

I am grateful to Dr. Michael Bailey for his support and research suggestions.

I wish to thank the School of Technology for the use of computers and laboratory space.

Most of all, I acknowledge the great debt that I owe my wife, JoAnne, for her patience and support during this long and arduous journey of exploration and self-discovery.

### TABLE OF CONTENTS

| 1 | Intr | oduction1                                      |

|---|------|------------------------------------------------|

|   | 1.1  | Computer Storage Systems                       |

|   | 1.2  | Common Memory Devices                          |

|   | 1.3  | Additional Memory Devices                      |

|   | 1.4  | Formulas                                       |

|   | 1.5  | Objective and Delineations                     |

|   | 1.6  | Hypothesis                                     |

|   | 1.7  | Methodology 18                                 |

|   | 1.8  | Overview of Remaining Chapters                 |

| 2 | Rev  | iew of Literature                              |

|   | 2.1  | Virtual Memory – an early pioneer              |

|   | 2.2  | Virtual Memory – the computer science approach |

|   | 2.3  | Virtual memory - an IT approach                |

|   | 2.4  | Solid State Devices – flash memory             |

|   | 2.5  | Solid State Devices – other options            |

| 3 | Met  | hodology                                       |

|   | 3.1  | Triangulation                                  |

|   | 3.2  | Theoretical Model                              |

|   | 3.3  | Published Data and Benchmarking 46             |

|   | 3.4  | Virtual Memory Simulation                      |

|   | 3.5                                                  | Physical Measurement                     | 48 |  |  |

|---|------------------------------------------------------|------------------------------------------|----|--|--|

| 4 | Rest                                                 | ults 51                                  |    |  |  |

|   | 4.1                                                  | Model Systems                            | 51 |  |  |

|   | 4.2                                                  | Theoretical Calculations                 | 55 |  |  |

|   | 4.3                                                  | Simulator Results                        | 56 |  |  |

|   | 4.4                                                  | Physical Measurement Results             | 58 |  |  |

|   | 4.5                                                  | Interpretation of Results                | 62 |  |  |

| 5 | Con                                                  | clusions and Recommendations             | 67 |  |  |

|   | 5.1                                                  | Conclusions                              | 67 |  |  |

|   | 5.2                                                  | Recommendations                          | 69 |  |  |

| 6 | Refe                                                 | erences                                  | 71 |  |  |

| A | Appendix A. Glossary77                               |                                          |    |  |  |

| A | Appendix B. Master Simulator Program Source Code     |                                          |    |  |  |

| A | ppendi                                               | x C. Slave Simulator Program Source Code | 85 |  |  |

| A | Appendix D. Physical Measurement Program Source Code |                                          |    |  |  |

### LIST OF TABLES

| Table 1-1 | Characteristics of Common Memory Devices                    | .6  |

|-----------|-------------------------------------------------------------|-----|

| Table 1-2 | Performance Characteristics of Three-Level Memory Hierarchy | 16  |

| Table 4-1 | Initial Information and Performance Data                    | .52 |

| Table 4-2 | Regression Results of SiSoftware Sandra Measurements        | .54 |

| Table 4-3 | Theoretical Calculations                                    | .56 |

| Table 4-4 | Simulator Results                                           | .57 |

| Table 4-5 | Physical Performance Measurements                           | .60 |

| Table 4-6 | Physical Performance Comparisons                            | .61 |

| Table 4-7 | Comparison of Results                                       | .62 |

### LIST OF FIGURES

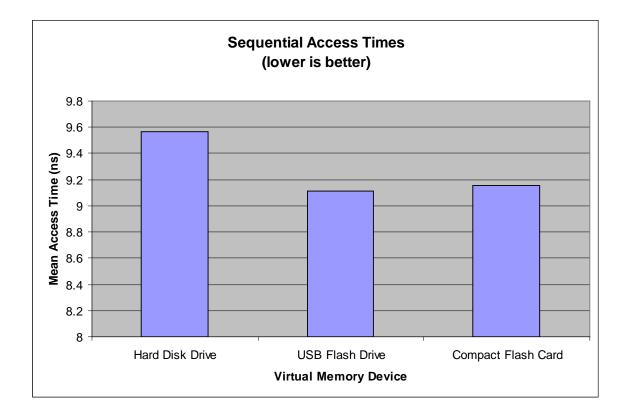

| Figure 4-1 | Sequential Access Times | 63 |

|------------|-------------------------|----|

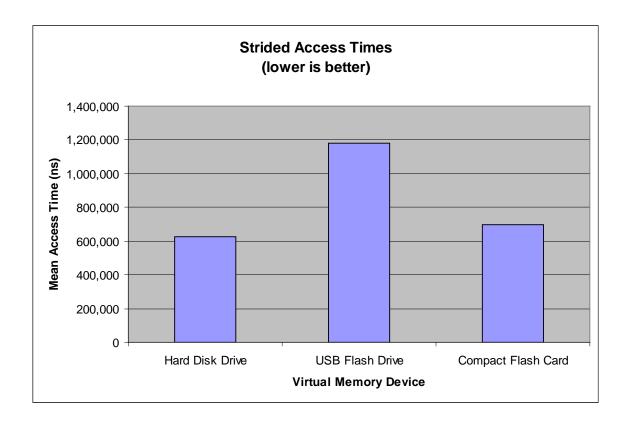

| Figure 4-2 | Strided Access Times    | 64 |

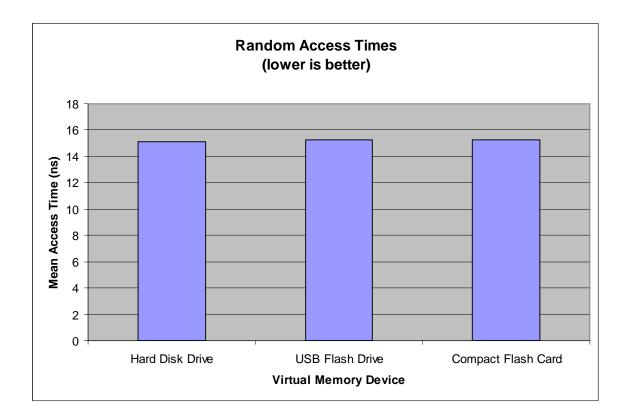

| Figure 4-3 | Random Access Times     | 65 |

xii

### **1** Introduction

Computer performance is more than a numerical analysis of numbers; it is also an aesthetic experience. The exhilaration of having a powerful machine respond to one's wishes is akin to the joy experienced at a musical concert or a ballet. Like all aesthetic experiences, a multitude of factors contribute to this experience:

- Computer architecture

- Actual computer hardware

- Operating system design

- Operating system configuration

- Application program design

- Application program configuration

- User proficiency

- User expectations

- User data stream

- The interactions between all these other factors

Part of the motivation for this thesis was a personal quest to recapture the thrill I experienced when I began programming in 1972. The platform was an IBM 1130 minicomputer, with 8kB of magnetic-core RAM. Input was programmed via a punched

card reader. Yet despite all its limitations, it was able to handle nearly any problem we could conceive for it. Why do our current computers not provide the same experience?

Our current home computers are far more powerful than the original supercomputers. For example, the Cray-1 had only 8MB of 50ns SRAM for its main memory, and the processor ran at only 80MHz clock speed. (Cray 1977, 1-3, 1-5). Yet the Cray-1 handled large scientific applications with ease. The question has troubled me: why cannot our current computers, with 64 times more memory, and 40 times faster processors, perform on a par with the Cray-1? Why do they seem so slow, particularly after sitting idle for a few hours, when switching tasks, or when an anti-virus programming is running in the background?

Part of the answers to these questions lies in the tasks that we set for our computers. The IBM 1170 was a single tasking machine. One and only one program could be run at a time. Similarly, the Cray-1 was a single-tasking vector processor, optimized for performing calculations on large data sets. With our complex operating systems, our current computers are expected to run 30-50 processes concurrently. Many of these processes are invoked by the operating system behind the scenes as services. Each time a new version of an operating system is introduced, the numbers and sizes of those processes increase. This in turn increases the demand for memory by the operating system. For example, Windows 2000 had a minimum memory requirement of 32MB, with 64MB recommended. (Microsoft 2007(1)). Windows XP requires a minimum of 64MB, with 128MB recommended. (Microsoft 2007(2)). Windows Vista Home Basic requires a minimum of 512MB. All other versions of Windows Vista require a minimum of 1GB of RAM. (Microsoft 2007(3)).

My target audience for this thesis was the home and small office computer users, who often cannot afford to upgrade their computers to meet the demands of their operating system. I had hoped to find a solution that would allow them to attain acceptable performance on older existing computers, and exhilarating performance on current machines.

A partial solution to the demand for larger amounts of memory is virtual memory, backed by the hard disk drive. However, the hard disk drive is a poor fit for virtual memory, as was noted by Peter J. Denning, an early pioneer in the field. (Denning 1970, 170). Its long latency delays often result in long delays for users, particularly when they use the multi-processing capabilities of their operating systems. Denning recommended the use of solid state memory devices for virtual memory, due to their shorter latency times. This prompted me to seek a solid state device that could replace the hard disk drive for virtual memory.

Every computer operation, at the lowest level, requires access to the storage system. Every instruction must be fetched from storage before it can be executed. Many computer instructions require fetching data from memory or storing data to storage. Because of its pervasiveness, the performance of the storage system affects the performance of every process, whether it is the operating system, a device driver or an application. Improving storage system performance has the potential to make dramatic improvement in overall computer performance. In turn, improving computer performance will improve the aesthetic experience for all users, even those with older machines.

#### **1.1** Computer Storage Systems

The storage system of a computer would ideally have: large capacity, high data density, low cost, high speed access, high data transfer rate, infinite read/write cycles, symmetric read/write access speeds, random access, low power consumption, nonvolatility, long-term stability, long data life, and ruggedness. Of course, no single storage technology exhibits all of these traits. It is for this reason that most computer systems have hybrid storage systems, with a combination of devices that together provide as many of these characteristics as possible.

Computer storage systems have three basic subsystems, each with differing purposes and requirements: permanent memory, secondary storage and working memory. Permanent memory contains the low-level code that enables the computer to commence operation in a known state, and requires nonvolatility, long-term stability, long data life, ruggedness and short read access time. It is most often constructed of read-only memory (ROM), although flash memory is becoming common to allow the low-level code to be updated without chip replacement.

Secondary storage stores programs and data that the computer is not currently using, but needs to access at some future time. This subsystem ideally requires large capacity, high data density, low cost, nonvolatility, long-term stability, long data life, infinite read-write cycles, and random access. Hard disk drives most often serve the secondary storage function, with CD-ROM or tape drives as backup.

The working memory subsystem is critical to the performance of a computer system, for it contains the programs and data that the computer is currently processing. The most important attributes of working memory are high speed access, high data

transfer rate, random access, infinite read/write cycles, symmetric read/write access speeds, low power consumption, large capacity and low cost. To achieve these attributes, working memory in most computers is constructed of multiple devices working together.

#### **1.2** Common Memory Devices

The most common devices used in working memory systems today are of three types: Static Random Access Memory (SRAM), Dynamic Random Access Memory (DRAM), and Hard Disk Drive (HDD). The characteristics of these memory devices are dramatically different, and are summarized in Table 1-1. The random access time is the delay between requesting a byte of data from a device and obtaining that datum from the device. The transfer rate is the rate at which a device can transfer sequential gigabits (10<sup>9</sup> bits) of data once the beginning byte of the sequence has been accessed. A more useful measure is sequential transfer time, which can be derived by dividing the transfer rate by 8 to scale it to gigabytes (2<sup>30</sup> bytes) per second and then taking the reciprocal, to calculate the time in nanoseconds (10<sup>-9</sup> seconds) required to transfer a single sequential byte. This calculated characteristic has been added to Table 1-1 for convenient reference.

In examining this table, the reader should note that the hard drive has a dual function in the typical computer system. It is the secondary storage system, storing programs and other files, for which it is very well suited. But it also acts as the lowest level of working memory, holding a paging file of active programs and data that cannot fit in the DRAM or SRAM. Hard drives have very few characteristics of the ideal working memory. The access time and power consumption are very high, and the transfer rate is very low. Their only redeeming virtues are their enormous capacity and their low cost per byte, compared to DRAM. While they are also nonvolatile, this is not a necessary requirement for working memory.

|                                       | SRAM          | DRAM     | HDD              |

|---------------------------------------|---------------|----------|------------------|

| Reference                             | (Samsung      | (Samsung | (Western Digital |

| Mitricite                             | 2007, 10, 13) | , U      | 2005)            |

| Capacity (MB = $2^{20}$ bytes)        | < 1           | > 1,000  | > 150,000        |

| Data density                          | low           | higher   | highest          |

| Cost                                  | highest       | lower    | lowest           |

| Access Time (ns = $10^{-9}$ sec.)     | > 6.6         | > 30     | > 4,000,000      |

| Transfer Rate (Gb/s = 10 <sup>9</sup> | >21           | >10      | < 0.7            |

| bits/sec)                             |               |          |                  |

| Sequential Transfer Time (ns =        | <0.4          | < 0.8    | >11.4            |

| $10^{-9}$ sec.)                       |               |          |                  |

| Block size (bytes)                    | 1             | 128      | 4,096            |

| Peak power consumption                | < 1.7         | < 0.6    | > 10             |

| (watts)                               |               |          |                  |

| Nonvolatility                         | No            | No       | Yes              |

| Ruggedness                            | Yes           | Yes      | Moderate         |

| Long useful life                      | Yes           | Yes      | Yes              |

| Symmetric read/write access           | Yes           | Yes      | No               |

| Random access                         | Yes           | Yes      | Yes              |

| Long-term stability                   | Yes           | Yes      | Yes              |

**Table 1-1 Characteristics of Common Memory Devices**

Note: Data obtained for fastest devices for which data was available. Hard disk drive transfer rate is buffer-to-disk sustained transfer rate.

The SRAM portion of working memory is called a "cache," which calls to mind the places where fur traders hid their pelts prior to sale. It thus means a nearby place to store something so that it can be retrieved quickly. In most modern computer systems, the cache is built in to the central processing unit, and thus cannot be readily modified. The DRAM portion of working memory is called "main memory" or "primary storage," as this is the level of memory where most of a computer's work is done. The hard drive portion is referred to as "virtual memory," implying that an illusion is created that main memory is larger than it really is.

To access a random byte of data in the hierarchy, the system first consults the cache, since if the data is found there, it can be retrieved in the minimum amount of time. If the datum is not found in the cache, main memory is searched. Only if the datum is not found in main memory does the system resort to the virtual memory. It should be noted the different portions of working memory overlap each other, such that all of the data in the cache is also contained in the main memory, and all of the data in the main memory is also contained in the virtual memory.

If data were only accessed a byte at a time, computer performance would be limited by the random access time of the level of memory where they are found. Indeed, the traditional calculation of average access time depends solely on random access times and "miss" rates. However, almost all memory devices have lower sequential transfer times than random access times, as illustrated in Table 1-1. So to minimize average access time, data is transferred in blocks from the slower levels to the faster levels to take advantage of the lower transfer times. When a faster level becomes full, the block least recently accessed is copied to a slower level and its place is freed up. This process is called *eviction*. The typical block size for each type of memory is listed in Table 1-1.

The assumption is made that when a datum is requested, the other data in the block are more likely to be requested in the near future, and when a block has not been recently accessed, the data in the block are less likely to be accessed. This assumption is called *locality of reference*. If it holds true, the data blocks most frequently accessed will migrate to the fastest level of memory, those least frequently accessed will migrate to the slowest level, and the average access time will approach a minimum value. Locality of reference is most likely to exist if data is requested sequentially. If the processor requests data in a strided access pattern, such that a new block must be accessed for each new byte that is requested, no locality of reference will exist and the average access time will approach its theoretical maximum. If data is requested in random order, the average access time will be somewhere between the minimum and the maximum. Formulas for calculating the sequential and strided access times are given in the next section.

Thus, when a datum is first accessed, not only it, but its neighboring data are copied from their current location into a region of the SRAM cache called a "line." When any data in that line is later required, it is accessed at the speed of the SRAM. Gradually the lines of the cache become full. When there is no longer any room in SRAM for data that the system wishes to store, the line containing the data least recently used is "evicted" from the cache: its values are copied into DRAM, and its place in the cache is made available. If the evicted data is then later required, its line must be again retrieved from DRAM, at a longer access time and a lower transfer rate.

A similar approach is taken with regard to virtual memory. Data in main memory are stored in regions called "pages." The system keeps the pages most recently accessed in DRAM, and evicts those pages that are least recently accessed to the virtual memory file on the hard disk drive. If a program requests data not found in DRAM, the page containing the requested data must be retrieved from the virtual memory, incurring a substantial delay due to its long access times and low transfer rates. This process is called a "page fault," and can have a substantial impact on the performance of the computer system. It is for this reason that the most common prescription for speeding up a slow computer is to add more main memory, so that the system does not have to use virtual memory as often.

#### **1.3 Additional Memory Devices**

A number of innovations have begun to be implemented to improve the performance of computer working memory systems. Most of them, such as Windows Vista ReadyBoost, USB flash drives, and solid-state disks (SSDs), are based on flash memory technology. These innovations will be discussed in more detail in Chapters 2 and 3.

#### 1.4 Formulas

The following formulas give the traditional calculation of average access time  $(A_{traditional})$ , and proposed calculations of average sequential access time  $(A_{seq})$ , and average strided access time  $(A_{stride})$  for a three-level hierarchy as described above:

$$A_{\text{traditional}} = R_c + 2R_m(P_m + P_v) + R_v P_v$$

(1.1)

$$A_{seq} = R_c + 2(R_m/B_m + T_m)(P_m + P_v) + (R_v/B_v + T_v)P_v$$

(1.2)

$$A_{\text{stride}} = R_{c} + 2(R_{m} + T_{m}B_{m})(P_{m} + P_{v}) + (R_{v} + T_{v}B_{v})P_{v}$$

(1.3)

where

A<sub>traditional</sub> is the traditional calculation of average access time from the entire hierarchy

$A_{seq}$  is the average time to access a byte of data from the entire hierarchy, when the data are accessed sequentially

$A_{\text{stride}}$  is the average time to access a byte of data from the entire hierarchy, when the data are accessed in a strided manner

$R_c$  is the time to access a random byte of data in the cache

$R_{\rm m}$  is the time to access a random byte of data in the main memory

$\mathbf{R}_{\mathbf{v}}$  is the time to access a random byte of data in the virtual memory

$P_m$  is the percentage of all unique data found in the main memory

$P_v$  is the percentage of all unique data found in the virtual memory

$B_m$  is the size in bytes of the data blocks in main memory

$B_v$  is the size in bytes of the data blocks in the virtual memory

$T_m$  is the time to transfer a sequential byte of data to or from the main memory

$T_v$  is the time to transfer a sequential byte of data from or to the virtual memory.

Equation 1.1 was derived from the formula given by Patterson and Hennessy for a two-level cache (Patterson and Hennessy 1996, 417), by extending it to a three-level hierarchy with a single-level page table. The first term,  $R_c$ , reflects that fact that all accesses are addressed to the cache first, since if the data can be found there, no other level of memory need be consulted. The second term,  $2R_m(P_m+P_v)$ , reflects that for all data not found in the cache, two accesses must be made to main memory, one to consult the page table to locate the data, and a second to read the data. This must be done for virtual memory data as well as main memory data, as the virtual memory data is copied from virtual memory into main memory, and then must be read back out again. The third term,  $R_vP_v$ , reflects that for data found only on the disk, the access time of the disk must be included. For simplicity, a single-level page table was assumed, located in main memory, which enabled the location of non-cached data to be determined with a single memory access.

Equation 1.1 is inadequate for modeling real world systems, in that it does not take into account the lower transfer times of memory devices when data is transferred sequentially. Equation 1.2 and Equation 1.3 were derived from Equation 1.1 to provide more realistic access times that include the transfer times and block sizes. Equation 1.2 estimates the average access time achievable when all data is requested sequentially. All of the data in a block is requested before another block must be accessed from the slower levels. This fully amortizes the access time of the block over the entire block. The first term, R<sub>c</sub>, is identical to the first term of Equation 1.1. The second term,  $2(R_m/B_m+T_m)(P_m+P_v)$ , reflects that for data not found in the cache, two pages of main memory must be read: one from the page table to locate the page where the data is found, and one which contains the data. The access time is averaged across the entire page, and the time to transfer each byte in the page is the transfer time of the DRAM. The third term,  $(R_v/B_v+T_v)P_v$ , reflects that for data located only in the virtual memory, a virtual memory page is copied to main memory. The time to locate the page is averaged across the entire page, and the time to transfer each byte in the page is the transfer time of the virtual memory.

Equation 1.3 was similarly derived from Equation 1.1, making the worst case assumption that data is accessed in a strided manner, such that a new block must be accessed for each byte requested. As before, the first term,  $R_c$ , is identical to the first term of Equation 1.1. The second term,  $2(R_m+T_mB_m)(P_m+P_v)$ , reflects that for data not found in the cache, two pages of main memory must be read: one from the page table to locate the page where the data is found, and one which contains the data. The access time and transfer time of the entire page is charged to each datum. The third term,  $(R_v+T_vB_v)P_v$ , reflects the access and transfer of a virtual memory page to access each datum located only in virtual memory.

It is helpful to compare these formulas with those proposed by Mekhiel and McCracken in 1994 (Mekhiel and McCracken 1994, 612, 613). They analyzed cache performance, citing Patterson and Hennessy for their methodology of extending standard performance formulas. Mekhiel and McCracken sought an alternative to trace-driven simulations to predict memory system performance. While their approach was specifically directed at caches, their formulas were strikingly similar to mine. Their approach is general enough to be applied to any memory hierarchy. It consists of building a decision graph, with a node for each decision to be made: instruction L1 cache miss, instruction L2 cache hit, instruction L1 cache miss, data L1 cache read hit, data L1 cache read hit, data L1 cache read miss, data L2 cache write hit, and data L2 cache write miss. Then, depending on the cache organization, memory/cache operations are assigned to each decision node. Probabilities and latency costs are assigned to each arc between nodes.

Average access time is calculated by adding the latencies of each arc, weighted by the respective probabilities.

The approach is almost identical to the Patterson and Hennessy approach, but is more generalized. The approach is best illustrated with the simplest example of a twolevel cache, where both caches are organized as "write-through" caches, that is, when data is written to any level of the memory, it is also written to all levels beneath it. The parameters of the model are:

$P_m$  = probability of executing a memory instruction

$P_1$  = probability of executing a load instruction

$P_s$  = probability of executing a store instruction

$M_{i1}$  = miss rate of the L1 instruction cache

$M_{i2}$  = miss rate of the L2 instruction cache

$M_{rd1}$  = read miss rate of the L1 data cache

$M_{rd2}$  = read miss rate of the L2 data cache

$M_{wd1}$  = write miss rate of the L1 data cache

$M_{wd2}$  = write miss rate of the L2 data cache

$P_{d1}$  = probability of a block being dirty in the L1 data cache

$P_{d2}$  = probability of a block being dirty in the L2 data cache

$L_1$  = number of clock cycles required to access the L1 cache

$L_2$  = number of clock cycles required to access the L2 cache

$L_{im}$  = number of clock cycles required to access the instruction memory

$L_{dm}$  = number of clock cycles required to access the data memory

B = cache block size for the L1 or L2 cache

The following additional parameters were derived from those listed above:

$H_{i1}$  = hit rate of the L1 instruction cache = 1 -  $M_{i1}$

$H_{i2}$  = hit rate of the L2 instruction cache = 1 -  $M_{i2}$

$H_{rd1}$  = read hit rate of the L1 data cache = 1 -  $M_{rd1}$

$H_{rd2}$  = read hit rate of the L2 data cache = 1 -  $M_{rd2}$

$H_{wd1}$  = write hit rate of the L1 data cache = 1 -  $M_{wd1}$

$H_{wd2}$  = write hit rate of the L2 data cache = 1 -  $M_{wd2}$

A "dirty" block refers to a block of data whose values have changed since being read from the main memory. Such a block must be copied back to main memory before its location in the cache can be made available for other blocks. The values of  $P_m$ ,  $P_l$ ,  $P_s$ ,  $M_{i1}$ ,  $M_{rd1}$ , and  $M_{wd1}$  were derived from a single level cache address trace. The values of  $L_1$ ,  $L_2$ ,  $L_{im}$ ,  $L_{dm}$  and B were design parameters, to be tested by the model. Only the parameter values of the L2 cache had to be estimated. Performance formulas were then derived from the decision graph of the model under consideration:

$$N_{cy} = N_{cyi} + N_{cyd} \tag{1.4}$$

$$N_{cyi} = (H_{i1})(1-P_m)L_1 + M_{i1}(H_{i2})(1-P_m)(L_1+L_2) + M_{i1}M_{i2}(1-P_m)(2L_2+L_{im})$$

(1.5)

$$N_{cyd} = P_1 P_m [H_{rd1} L_1 + M_{rd1} H_{rd2} (L_1 + L_2) + M_{rd1} M_{rd2} (2L_2 + L_{im})] + P_s P_m L_{dm}$$

(1.6)

where

$N_{cy}$  = average number of cycles to access data from the entire hierarchy

$N_{cyi}$  = average number of cycles to access the instruction cache

$N_{\text{cyd}}$  = average number of cycles to access the data cache

On the surface, these formulas bore little resemblance to mine. However, on careful examination, several parallels were drawn. The process of identifying a separate term for each component of memory access time, and then weighting that time based upon percentages is almost identical to the process I used to derive my formulas. The latencies of the different levels of the hierarchy figured very prominently in these formulas, as they did in mine.

The differences were also significant. They were targeted specifically toward caching systems, and did not take into account the block transfer times or other specific characteristics of virtual memory. Mekhiel and McCracken also relied upon simulation data to estimate cache miss rates, which my model did not require.

To illustrate the application of my formulas, I configured a "typical" older computer. The cache and the main memory were assumed to have the sizes listed in Table 1-1 and to be full of useful data. A fully utilized virtual memory of 1.5 times the size of main memory was also assumed. Table 1-2 repeats the performance parameters from Table 1-2, gives the derived values of  $P_m$  and  $P_v$  and the resulting values of  $A_{traditional}$ ,  $A_{seq}$  and  $A_{stride}$ .

|                                                                           | Cache     | Main   | Virtual     | Access Time |

|---------------------------------------------------------------------------|-----------|--------|-------------|-------------|

|                                                                           |           | Memory | Memory      |             |

| Size (MB = $2^{20}$ bytes)                                                | 1         | 1,000  | 1,500       |             |

| (R)andom Access Time (ns)                                                 | 6.6       | 30.0   | 4,000,000.0 |             |

| (T)ransfer Time (ns)                                                      | 0.4       | 0.8    | 11.4        |             |

| (B)lock size (bytes)                                                      | 1         | 128    | 4,096       |             |

| (P)ercentage of data                                                      | .001      | .666   | .333        |             |

| Average Access Time (traditional calculation) $(A_{traditional})(\mu s.)$ |           |        |             | 1,332.067   |

| Sequential Access Time $(A_{seq})(\mu s)$                                 |           |        |             | 0.337       |

| Strided Access Time (Astride)(                                            | 1,354.163 |        |             |             |

| Average Access Time $(A_{ave})(\mu s)$                                    |           |        |             | 677.250     |

Table 1-2

Performance Characteristics of Three-Level Memory Hierarchy

Note: Data derived from Table 1 and from Equations 1.1, 1.2 and 1.3

To calculate an accurate average access time, one must measure the access patterns to determine how many of the accesses fit the sequential access pattern, how many fit the strided access pattern, and how many fall somewhere in between. But a rough estimate can be made by assuming that a random access pattern approximates the performance of a real virtual memory system. This assumption seems reasonable for multi-threaded operating systems, such as Windows 2000 or Windows XP, where 30 to 50 processes may be executing simultaneously, each accessing memory independently. The mean of the sequential and strided access patterns was taken to be an estimate of the access time when a random pattern is applied., as reported in Table 1-2. This average access time is heavily influenced by  $R_v$ , the random access time of the virtual memory. If  $R_v$  could be reduced by 1/2, the average access time would drop to 333.810us. This could improve computer performance significantly.

All computer systems have a finite amount of main memory that they can accommodate, yet applications and operating systems continually need more working storage memory. The common solution for this dilemma is to devote a portion of the hard disk drive to virtual memory. The motivation of this thesis was to find an alternative form of virtual memory that would have a lower random access time than hard disk drives. This would enable home and small office computers to run advanced applications and operating systems at acceptable speeds, despite their inherent memory limitations.

#### **1.5** Objective and Delineations

The purpose of this research was to find an alternative to the hard drive for virtual memory for home and small office computers that would reduce average access time of the entire working storage subsystem. It was assumed that such a solution would be based upon solid-state electronic devices of some kind rather than mechanical.

One alternative that was not explored was simply increasing the size of main memory. While this is an obvious solution, it is expensive and is limited by the memory slots on the computer system being evaluated. Rather, a solution was sought which would be generally applicable to almost any computer, regardless of its memory constraints.

Nor did I investigate the effects of hard drive caches. While this is becoming increasingly common, the sizes of such caches are so small relative to the size of virtual memory, I felt that they would be of marginal benefit.

Also excluded from the investigation were software-based solutions, such as Windows ReadyBoost and other operating system improvements. The purpose was to focus on improving the hardware, and leave to other efforts increasing the efficiency of the software that must run on it.

I also did not investigate alternative operating systems such as Linux, as most home and small business computers today run some version of Microsoft Windows.

## 1.6 Hypothesis

I attempted to disprove the following null hypothesis:

The performance of a computer does not improve when harddrive virtual memory is replaced with other virtual memory options, such as solid-state memory.

## 1.7 Methodology

I developed the following procedures in pursuing this research:

1. Analyze the datasheets and other literature of various solid-state electronic

devices currently available for use as computer storage. The following

candidates were identified:

- Graphics cards, with embedded processors and memory

- FPGA cards, with programmable logic devices and memory

- Flash memory cards

- USB Flash drives

- Solid-State Disk devices, using DRAM or Flash as a simulated hard drive

- 2. Select those of the above devices which meet the following criteria:

- It must use a standard interface found in most commodity computers, such as PCI bus, USB, or IDE.

- It must provide at least 1GB of storage capacity, as this is a minimum practical size for virtual memory.

- It must provide published or tested random access times of not more than 1 ms, in order to provide performance improvement over a hard disk drive

- It must not cost more than \$200. I chose this figure as the approximate cost of replacing a motherboard and adding additional system DRAM.

This is the major competitive alternative to virtual memory.

- It must not consume more than 15 watts of power. This is because the older computers that I am targeting have limited power supplies.

- 3. Acquire a representative sample of the selected devices.

- Develop a model which can estimate the performance of the different devices acquired when used for virtual memory. The formulas presented above constitute this model.

- 5. Develop a simulator of a virtual memory system, against which sequential, strided, and random access patterns are applied.

- Validate the model and the simulator by developing and running custom benchmarks to measure the actual performance of the devices that have been acquired.

### **1.8** Overview of Remaining Chapters

Chapter 2 summarizes related research and the datasheets and other documents that were evaluated to select the test devices. Chapter 3 presents details regarding the derivation of the formulas of the theoretical model, motivation and design considerations of the simulator and the physical measurement benchmarks used to evaluate the selected devices. Chapter 4 sets forth the test results. Chapter 5 gives conclusions and proposals for future research. The Appendices contain a Glossary of commonly used terms, and the source code of the custom programs that were written to simulate and measure virtual memory system performance.

# 2 Review of Literature

### 2.1 Virtual Memory – an early pioneer

No discussion of virtual memory would be complete without mention of Peter J. Denning. While he did not originate the concept, as he freely acknowledged, his was the first full analysis of its performance, and his "Working set model" was the first rigorous explanation of the phenomenon of thrashing (Denning 1968).

Although he used a fair amount of calculus, Denning's paper on the "Working Set Model" was very readable. His conclusions were clear and intuitively appealing:

- Each process can operate efficiently with a subset of its total memory requirements resident in main memory. This subset is its "working set." The working set is most conveniently measured in pages.

- 2. While the contents of the working set of a process will vary with time, the size of the working set will remain somewhat constant over an interval approximately equal to twice the time that it takes to transfer a page to or from the auxiliary storage device. This interval is known as the "working set parameter."

- 3. The size of the working set of each process is best determined by the operating system by measuring its memory requirements over time.

21

- 4. Thrashing occurs when the total size of the process working sets exceeds the amount of main memory available.

- 5. System performance can be improved by balancing the total working set size with the amount of main memory available.

Although this paper did not derive concrete formulas of memory performance, it did set the stage by discussing "paging" in quantitative terms.

Denning's subsequent paper, entitled "Virtual Memory," (Denning 1970), was a thorough exploration of all of the issues surrounding virtual memory. He began with a history of the concept, beginning with manual memory management using overlays, and then static memory management using intelligent compilers. Four developments in software design and six developments in system design provided more power and flexibility but made the problem of memory management much more difficult. The software developments were:

- 1. High-level programming languages insulated programmers from the details of the machines on which the programs were running.

- Machine independence, a logical extension of high-level languages, allowed hardware changes without reprogramming, and allowed programs to run on different machines.

- 3. Program modules which are compiled separately and not linked together until run-time became the accepted method of decomposing complex programs into manageable pieces, allowing programming teams to work together on a single project, and sharing code pieces and algorithms between projects and programmers.

22

4. List processing languages enabled programmers to structure their data in more flexible ways, without predetermining the size of their data structures.

The system developments, arising primarily from timesharing and multiprocessing environments were:

- 1. The ability to load a program into a space of arbitrary size.

- 2. The ability to run a partially loaded program.

- 3. The ability to modify the amount of space used by a running program.

- 4. The ability to relocate a running program into different regions of memory.

- 5. The ability to schedule the execution of a program to run at a particular time.

- 6. The ability to change system equipment without reprogramming or recompiling.

The difficulties these developments created for memory management caused scholars to call for some form of dynamic memory management, where memory allocation would change at run-time, as needed. One approach left memory management to the programmer, using "allocate" and "deallocate" commands. Another approach held that the problem had become too difficult for programmers to manage, particularly in a multiprogramming environment, and thus called for some form of automatic memory management.

Denning credited the Atlas project at University of Manchester with originating the idea of automatic management of a two-level memory hierarchy as if it were a single level store by dissassociating logical addresses from physical addresses. The Atlas proposal inspired virtual memory systems in the IBM 360/85 and the Burroughs B6500 and many other computer systems. But virtual memory had its own share of problems:

- Many programmers clung to the notion that they could improve the speed of their programs by increasing the memory requirements. Yet this might not be the case in a virtual memory system, since the available memory is largely an illusion. Unnecessarily large and carelessly organized programs increase the overhead for the virtual memory system.

- Nonpaged memory systems suffer from fragmentation of the memory space, which reduces the available storage capacity.

- 3. Since most systems do not load pages into main memory until they are requested, they often suffer severe delays during program loading.

- Many systems are subject to thrashing, where total system performance collapses.

Denning then introduced two memory performance parameters: memory reference time,  $\Delta$ , which represented the delay between references to main memory, and transport time, T, which represented the time needed to complete a memory transfer between the levels of memory. Of particular interest was the ratio between these two parameters. He contended that the ratio was approximately 10<sup>4</sup>. It should be noted that this has changed in the years since his paper was written. Main memory now responds within 30ns, while disks have an average access time of at best 2.9ms. If it can be assumed that these access times approximate  $\Delta$  and T, the ratio is now closer to 10<sup>5</sup>.

Denning then calculated the optimum size for virtual memory pages for maximum storage efficiency. Given the average size of a segment at 1000 bytes, the optimum page size would be 45 bytes, assuming the storage ratio of  $10^4$  cited above.

He then calculated the optimum size for the high transfer times of drums and disks, and concluded that disks were unsuitable for virtual memory, drums were marginal, and solid-state devices were the best alternative. With the widening performance gap between DRAMs and hard disk drives, as noted above, these conclusions are even more persuasive.

He also looked at replacement policies and classified them as "local" if pages can only be evicted by pages from the same process and "global" if pages can be evicted by pages from any process. He contended that an optimal policy would be local only, and that global policies would always be suboptimal, as they cannot determine when memory is overcrowded, or guarantee that each process will have continuous access to its working set, and are subject to thrashing. He then derived a formula for calculating when thrashing will occur.

Assume that *k* programs are in memory

Each program *i* has an average workspace of  $m_i$  and an expected fault rate of  $f_i(m_i)$ , such that as  $m_i$  decreases,  $f_i(m_i)$  will increase

Let  $d_i(m_i)$  be the "duty factor" or expected fraction of time that process *i* spends in execution, calculated as:

$$d_i(m_i) = \left[\Delta / f_i(m_i)\right] / \left[\Delta / f_i(m_i) + T\right]$$

(2.1)

Let  $\alpha$  be  $T/\Delta$ , then

$$d_i(m_i) = 1/(1 + \alpha f_i(m_i))$$

(2.3)

If  $\alpha$  is very large, then unless the fault rate is extremely small, the duty factor will be very small, and the more time the process will spend waiting for memory. If the processes are all in equilibrium, such that their fault rates are at a minimum, and one more process is initiated, the workspace of each of the existing processes will have to be reduced to make room for it, which will cause the fault rates to rise sharply, the duty factors to fall, and thrashing to occur.

Most research on virtual memory since Denning has focused on minimizing thrashing by minimizing fault rates. The other solution would be to reduce the  $\alpha$  factor, by changing the technology used for the auxiliary storage. This was exactly what my thesis proposed to do.

Denning's analyses have proven so helpful that he continues to be cited by researchers today. In 1996, the Association for Computing Machinery, which calls itself "the world's oldest and largest educational and scientific computing society," published a special edition of *ACM Computing Surveys* to commemorate the 50th anniversary of its founding. The focus of the issue was "strategic directions in computing research." Denning was invited to present an overview of the history of virtual memory, which demonstrates the esteem in which his work is held. (Denning

1996). A year later, the Institute of Electrical and Electronics Engineers honored Denning by publishing a similar essay in their book, *In the Beginning: Recollections of Software Pioneers*. (Denning 1997).

### 2.2 Virtual Memory – the computer science approach

Despite Denning's conclusions, magnetic drums became extinct. Although main memories grew in size, programmer demands for memory increased faster. The most common secondary storage system on computer systems became the magnetic or "hard" disk. So it was natural to use the hard disk drive for virtual memory to meet the demand. Because of their enormous latency, most of the early research was devoted to finding ways to make software exhibit more locality of reference, to minimize the number of page faults.

I call this the computer science approach to virtual memory, since it was characterized by highly theoretical models and analysis of algorithms. Typical of this research was a paper published in 1987 by Aggarwal, Alpern, Chandra and Snir, researchers at IBM's T. J. Watson Research Center. (Aggarwal et al. 1987) They proposed a theoretical model for the study of memory hierarchies. Rather than attempt to model actual systems, a simplified model was developed. Each memory location x was assumed to have an access time of  $ceiling(log_2x)$  units. This would create a hierarchy consisting of 1 storage word with 0 access time, 1 word with access time of 1 time unit, 2 words with access time of 2 units, etc. They then demonstrated the need for locality of reference in programs in order for them to run efficiently in this hierarchy. They derived complex proofs of theoretical performance of various algorithms on this

hierarchy. But none of these formulas translate readily into calculation of the performance of real systems.

The Hierarchical Memory Model presented in Aggarwal's first paper was inadequate in that it did not include the effects of collecting data into blocks for transfer from one level to another. Later that same year, three of the original researchers rectified this deficiency in a follow-up paper, (Aggarwal, Chandra and Snir 1987), presented at the 28th Symposium on Foundations of Computer Science. Unfortunately, it suffered from the same defect as the original paper in that it is only roughly analogous to real systems.

Two researchers at Leiden University extended the Hierarchical Memory Model even further in 1994. They introduced the concept of parallelism, such that transfers between different levels may occur simultaneously. Similar to the work of Aggarwal, et. al., it involves theoretical proofs of performance of various algorithms in a hypothetical machine, with no attempt to validate the model with measurements on a real machine. (Juurlink 1994).

The computer science approach was taken to new extremes in 2002 by Albers, Favrholdt and Giel. Elaborate models were developed to generate address sequences, to measure the working sets of these sequences, and then to calculate the fault rate of various virtual memory algorithms. Again, the models were based upon abstract families of functions, and highly theoretical proofs of upper and lower bounds on the fault rate were presented. To their credit, they sought to validate their calculations with real world measurements. However, these measurements were not of performance, but of address sequences, working sets, and fault rates. (Albers, Favrholdt and Giel 2002).

28

## 2.3 Virtual Memory - an IT approach

In 1990, Patterson and Hennessy published the first edition of their classic text, and presented to the world a more practical approach to the issue of computer performance. (Patterson and Hennessy 1990). As they stated in the Preface to their Second Edition,

[W]e hope to demonstrate what we stated about computer architecture in our preface to the first edition: It is not a dreary science of paper machines that will never work....

Our primary objective in writing our first book was to change the way people learn and think about computer architecture. . . . The field is changing daily and must be studied with real examples and measurements on real machines, rather than simply as a collection of definitions and designs that will never need to be realized. (Patterson and Hennessy 1996, xiii).

I call the Patterson and Hennessy methodology the "IT approach," as it emphasizes real world performance modeling and measurement, rather than theoretical constructs and theorems. Their text is perhaps the most actively cited source on computer performance today.

Bowen Alpern, one of the co-authors of Aggarwal's original paper on the Hierarchical Memory model, published a paper in 1994 that represented a similar shift in thinking. (Alpern et al. 1994). Alpern and his co-authors recognized the limitations of theoretical computer science, and its failure to address the performance characteristics of real computer systems. As had Denning, Alpern and his team recognized that the performance of such systems was largely determined by the speed of the different levels of memory, and that the performance gains to be obtained by reducing the rate of page faults were limited by the these physical limits. They presented a realistic assessment

of the characteristics of real memory systems, including such parameters as block size, block count, and latency.

They proposed a model which would capture these characteristics for the purpose of tuning the performance of programs to particular machine architectures, the Memory Hierarchy model, which involves maintaining parameters for each level of memory: block size, number of blocks, and transfer time of each level. They then simplified the model by assuming constant packing factors and aspect ratios, and transfer time determined by a simple function, usually a constant, an identity or an exponential. They called this model the Uniform Memory Hierarchy. The communication efficiency of a program is determined by determining its RAMcomplexity and its UMH-complexity and taking the ratio. A program is considered communication efficient if its ratio is greater than 0. The ratio is largely determined by the transfer cost function, which is their term for transfer time of a block of data from one memory level to another. Unfortunately, the paper then degenerated into complex theoretical proofs, similar to Aggarwal's approach, with no empirical validation of their theories. (Alpern et al. 1994, 15)

Another team of investigators also recognized the need for simpler formulas for predicting cache performance. (Mekhiel and McCracken 1994). They analyzed cache performance, citing Patterson and Hennessy for their methodology of extending standard performance formulas. Mekhiel and McCracken sought an alternative to tracedriven simulations to predict memory system performance. Trace-driven simulations were considered to be the most accurate method of determining system performance, but were very time-consuming to perform. Prior studies of cache performance had

30

focused on only a few parameters. Their model looked at line size, cache size, write strategy and latency and estimated performance based on the statistical output of a trace-driven simulation. They then analyzed a two-level cache system and validated their results against a trace-driven simulation of a two-level cache. While their approach was specifically directed at caches, their formulas were strikingly similar to those I derived for a complete memory hierarchy, as noted in Section 1.4

#### **2.4** Solid State Devices – flash memory

Flash memory has been around a long time, and recently has been touted in popular computer literature as a replacement for the hard disk drive. Indeed, some computer systems are now being sold with flash drives instead of hard disk drives. It has been investigated formally at least twice as an alternative to hard drives for portable computers. (Douglis et al. 1994; Tseng, Li and Yang 2006). The Douglis paper sought an alternative to the hard drive for secondary storage in mobile computers. The main disadvantages of the hard drive it identified were its high power consumption and its slow spin-up time. The authors investigated two forms of flash memory: flash-based disk emulators and flash memory cards because of their low power consumption, low latency, and high throughput for read transactions. The methodology was two-fold: hardware measurements using "micro-benchmarks" and trace-driven simulations. The results showed that flash memory used 1/10 the power of similarly sized hard drives. Performance results were mixed. While average read performance was better for flash memory devices, average write performance was worse, unless free space in the flash was kept available by aggressive erasure of deleted files. This paper differed from my thesis in that it was specifically focused on file system performance rather than virtual memory, and was also focused on mobile computers. Also, the paper is somewhat old, and its measurements are therefore no longer relevant. Nevertheless, their methodology was very helpful. In particular, the "micro-benchmarks" were similar to my custom benchmarks, which I will discuss in Chapter Three.

The Tseng paper looked at flash memory devices for their power-saving potential, and did not address the performance benefits. The authors noted that traditionally, virtual memory has been designed assuming that a hard disk drive would serve as the secondary storage. As flash memory improved its capacity, reliability, and power consumption, it became an increasingly feasible replacement for the hard drive in virtual memory systems in portable computers. But they warned that its characteristics were so different from those of a hard drive, a virtual memory system needed to be designed differently to make it energy efficient. Virtual memory systems typically used a 4kB page size, which was 8 times the size of a flash memory page. Writing full 4kB pages back to the flash when they were evicted from main memory was wasteful of energy and flash endurance. If virtual memory pages were divided into 512B subpages, 50% fewer writes would be required, resulting in up to 20% energy savings. While this paper was more current than the Douglis paper, it was of limited benefit to me in that it did not address the performance benefits of flash memory. It does appear that the subpaging technique they describe could benefit performance by reducing the number of writes required.

In 2002, Christopher Tacke published a white paper for Applied Data Systems in which he analyzed the performance of a particular flash disk emulator, FlashFX by

32

Datalight. (Tacke 2002). It supplemented Datalight's qualitative white paper by providing quantitative measurements. The measurements were done on an embedded system running Windows CE. A 32MB flash memory was partitioned to present a 4MB flash drive to the operating system. The benchmark program wrote an empty file, and then added 256 byte additions to the file until the disk was full. The time of each write operation was recorded. The results showed that 18,117 write operations involved no garbage collection, and took an average of 5.5ms to complete. 555 writes required garbage collection and took an average of 1797ms. The rate of garbage collection started at 1 per 200 writes, and increased steadily to 1 per 20 writes at 20% utilization. The garbage collection then started cycling between a high of 1 per 3 writes and a low of 1 per 40 writes. Not only did the rate of garbage collection increase, the time required for garbage collection also started increasing from 1300ms to 1800ms, with spikes as high as 3700ms. Tacke concluded that flash write performance reaches a steady state at about 25% utilization. Nevertheless, write performance is subject to While his data was focused on embedded systems, and slow wide variations. technology flash, his methodology was sound.

Flash memory devices come in a variety of packages. This thesis investigated both USB flash drives, because they are so common, and Compact Flash cards, because of their potential for higher bandwidth. Since most desktop systems do not have Compact Flash connectors, I sought adapters that would allow desktop systems to use Compact Flash cards. Two adapters were investigated: the Addonics SATA CF adapter (Tom's Hardware 2005) and the ACS IDE CF adapter (Ackerman Computer Science 2006). The editors of *Tom's Hardware*, a website devoted to computer hardware, measured the performance of the SATA CF Adapter by Addonics to compare its performance to that of Compact Flash card readers that connect to a computer via USB. The read and write performance was only slightly better than USB card readers (7.9 MB/s v. 7.6 MB/s read, 7.4 MB/s v. 6.8 MB/s write). However, the latency was significantly better (0.2ms v. 0.6ms). While this adapter might be of interest, it was not selected for physical evaluation as it required a SATA interface.

The ACS adapter was more versatile, as it did not require a SATA connector, but Ackerman Computer Science (ACS) provided no performance data. Significantly, ACS recommended against using flash memory for virtual memory applications due to its limited endurance. A number of other people have expressed similar concerns. But actual measurements have shown such fears to be unfounded. For example, Marsh, Douglis and Krishnan measured the expected wear rate of flash memory in a file caching application, and found that even the least durable flash devices should last at least 33 years. (Marsh, Douglis and Krishnan 1994).

In a press release dated April 25, 2005, Samsung announced that its OneNand flash memory would be featured in the first fully functional Hybrid Hard Drive (HHD) designed for Windows Vista. (Samsung Electronics 2005). It combined the data density of the magnetic rotating disk with the low-power, reliability and fast read/write access times of flash memory. The 1Gbit (128MB) flash memory acted as a write buffer and boot buffer for the hard drive. The hard drive was kept spun down while data is written to the flash memory. Only when the flash memory was full did the disk spin up so that the data in the flash memory could be written to the disk. By keeping

the disk spun down most of the time, power was reduced 95% and operating temperatures were minimized, enhancing disk reliability. While faster boot times were claimed, no specific data was provided regarding this feature. The HHD was specifically targeted toward mobile computers, where power consumption is critical. Samsung admitted that the HHD will be more expensive than conventional hard disk drives, but claimed that the benefits would be worth the additional cost. While this device was not evaluated for this thesis both because of the lack of specific performance data and because of the high cost of the hybrid device, it did demonstrate that other researchers consider flash memory to be appropriate for improving the performance of hard disk drives.

Flash memory devices are under constant scrutiny and testing by third parties. Scott Clark, Consumer Editor for *Everything USB*, an online magazine devoted to USB devices, has done a series of performance tests of flash USB drives, using SisSoft Sandra, an open source benchmark product. (Clark 2005(1); Clark 2005(2); Clark 2006; Clark 2007). Of all the published data regarding flash memory performance, Clark's is the most rigorous. He documents his benchmark program and publishes the full data produced by it. As performance was important for my thesis, I relied upon his articles in selecting flash memory devices and benchmark software for the physical evaluation portion of my research.

The first article examined Lexar's flagship product, the JumpDrive Lightning USB drive. Despite its name, it was less speedy than other flash drives. It excelled at transferring large files (23MB/s read bandwidth for 64MB files), but performed poorly on smaller files (.434MB/s read bandwidth for 512B files). No value was given for

latency, but it can be estimated from the 512B file performance, since 512B represents the minimum block size. Taking the reciprocal of this figure gives a latency value of  $2.3\mu$ s (10<sup>-6</sup> seconds).

While the Lexar JumpDrive Secure II 1GB USB drive evaluated in the second article is marketed primarily for its security features, it also had superior latency performance compared with the JumpDrive Lightning. Read performance for 512B files was .545MB/s, from which I estimated the latency to be 1.8µs. It performed even better in encrypted mode, probably due to the smaller cluster size used by the encrypted mode (4kB v. 16kB for the regular mode).

The third article evaluated the SanDisk Cruzer Titanium 2GB USB drive. Its performance is respectable, although not as fast as that of the Lexar drives, (read bandwidth of .397MB/s for 512B files. Using the estimating procedure set forth above, I arrived at 2.5µs latency. This access time is more than 1,000 times lower than that for the fastest hard drives available for personal computers. I selected this flash drive as one of my test devices due to its acceptable performance and outstanding durability.

Corsair Flash Voyager GT 4GB Flash USB Drive, reviewed in the fourth article, outperformed the Lightning and the Secure Disk II, even on the large file transfers, (32MB/s on 64MB files). Its latency was also impressive (2.669MB/s bandwidth for 512B files, yielding an estimated 374ns latency). Achieving this latency was no doubt due in large measure to its 4kB cluster size.

Rob Galbraith, the owner of *Rob Galbraith Digital Photography*, maintains a database of Compact Flash card performance in cameras and in PCs. (Galbraith 2006(1); Galbraith 2006(2)). Last year, he evaluated the performance of the SanDisk

Extreme IV Compact Flash card, which at that time was twice as fast as the nearest competitive card. The secret to its speediness was that its controller supports Ultra ATA/66 mode, otherwise known as Ultra DMA Mode 4, the first card to do so. The measured speed was 38.611 MB/s in transferring data from the card to a PowerMac G5 over a Firewire 800 port to a 500GB RAID 0 array. The speed of transferring data from the flash card to RAM should be even more impressive. I chose this Compact Flash card because of its speed.

The fastest flash devices I was initially able to identify were flash disk modules from Adtron Corporation in Phoenix, AZ. These modules were packaged in a case shaped like a hard drive, obviously designed to fit in a 3.5" drive bay, with a hard disk drive interface. The datasheet listed transfer rates of 65MB/s read, 60MB/s write, and burst transfer rates of up to 100MB/s. (Adtron) This was even faster than most hard drives. The endurance was also tested to be very high: 5,000,000 write/erase cycles, which is 5 times the endurance claimed for other flash devices. Unfortunately, the datasheet gave no details of the internal structure of the device, how it attained such speeds, or what its latency was. The cost is also a limiting factor: prices start at \$1,235 for a 1GB drive. The absence of latency data and the high cost excluded this device from further consideration.

Recently, more reasonably priced solid-state flash drives have become popular. One of the most interesting was the X-25M, by Intel. It was tested by the researchers at *Tom's Hardware* to have read transfer rates of 200 MB/s, write transfer rates of 70 MB/s and read latency of less than 100µs. It achieved the astounding read characteristics by use of a controller with ten data channels, one to each of ten flash memory chips, and a 16MB DRAM cache. (Schmid and Roos 2008). They reported that Intel was intending to sell it for \$595 in quantities of 1,000. A quick check of current prices showed it selling for \$324 for an 80GB drive. While it is priced too high for use solely as a virtual memory device, it would certainly be of interest as a hard drive replacement for laptop computers. Other solid state drives are more moderately priced, but have performance characteristics similar to the Compact Flash cards which I had already acquired. (Newegg 2009)

While not strictly speaking a flash technology, I cannot ignore ReadyBoost, a software feature built into the Windows Vista operating system. This technology uses a USB flash drive as a read cache for the hard disk drive, hoping to capitalize on the lower latency of flash memory. Tests of ReadyBoost have shown it to be of marginal benefit for systems with 512MB of RAM, and of almost no benefit for systems with 1GB of RAM or more. (Sun 2007). This was not considered for serious investigation as Windows Vista is not commonly found on home or small office computers. As a sidelight, Windows 7 beta testers have reported that ReadyBoost makes a much bigger impact than it did in Vista. (Kneen 2009).

## 2.5 Solid State Devices – other options

Other solid-state devices were investigated for feasibility. I evaluated a hardware RAMdisk, called "i-RAM," manufactured by Gigabyte of Taiwan. Patrick Schmid, writing for *Tom's Hardware*, evaluated the i-RAM as a replacement for hard drives. (Schmid 2005) While the concept was not new, the price of this particular unit was. Prior DRAM-based devices had been targeted at commercial applications, costing

thousands of dollars. i-RAM was packaged as a PCI form factor card, with four DIMM slots and backup battery for \$150.00. This made it possible to populate it with spare memory modules for a very low price. The interface was SATA-I, so it could be installed in current commodity PCs, but not in older computers that relied on the IDE interface for their hard drives. Its memory controller was a Xilinx FPGA. The backup battery only preserved the data for a maximum of 16 hours, but was only called upon if power was interrupted to the case. The computer did not have to be powered up for the i-RAM to remain powered. The memory clock ran at 100MHz, allowing a DDR data rate of 200MHz. Maximum speed was obtained when only one or two modules were installed.

Several installation problems were identified. First, the card required a 5 volt PCI slot, while current computers have 3.3 volt slots, often in a PCI-X configuration. Second, the card was so wide that it overlapped the neighboring slot, making it unusable. Finally, the card required the host computer to have a spare SATA interface.

These installation difficulties were overcome, and the performance benefits were enormous. The latency of i-RAM was measured at 50ns, compared to 5.75ms for the fastest hard drive in the study, a Maxtor Atlas 15K drive, with a spindle speed of 15,000 rpm. Average read throughput of i-RAM was 126MB/s, compared to 64MB/s for the Maxtor.

Because of the installation issues, which would make it less practical for commodity personal computers, I did not purchase an i-RAM for performance evaluation.

39

# 3 Methodology

## 3.1 Triangulation

To assure validity of the results of this research, a triangulation approach was applied. First, a theoretical model of performance of a memory hierarchy was developed. This model was derived from standard cache performance formulas presented by Patterson and Hennessy in their classic text. (Patterson and Hennessy 1996, 417). Second, a simulator based upon this theoretical model was designed to project performance of typical software applications on memory hierarchies of different criteria. Actual performance parameters of different devices were researched from independent testing websites for use in this simulator. Third, two actual flash memory devices with representative performance characteristics were acquired and their performance was measured using industry standard benchmark software to verify the published data. Finally, the benchmark software used in the simulator was also applied to these devices to validate the accuracy of the simulator. More details of each leg of this approach are presented below.

## 3.2 Theoretical Model

The model began with the formula given by Patterson and Hennessy for twolevel caches, for the reason that they gave no formula for virtual memory performance, implying that the formula would be analogous to that for caches:

$$A_{mem} = H_{L1} + M_{L1} x (H_{L2} + M_{L2} x P_{L2})$$

(3.1)

where:

$A_{mem}$  = Average memory access time  $H_{L1}$  = Hit time for first level cache  $M_{L1}$  = Miss rate for first level cache  $H_{L2}$  = Hit time for second level cache  $M_{L2}$  = Miss rate for second level cache  $P_{L2}$  = Miss penalty for second level cache

This formula was adjusted for a number of reasons. First, the term "miss rate" seemed inappropriate for virtual memory. Instead, a more generic term "Percentage of Data" was chosen for the model. One obvious advantage of this term was that it was easily calculated from the size of the various levels of the memory hierarchy. Using miss rates would have required measurement from a simulator using address traces. For cache design, miss rates are very important. Much literature has been devoted to classifying miss rates into "compulsory miss rate," "capacity miss rate," and "conflict miss rate," and analyzing the impact of various cache organizational parameters such as cache size and associativity on these rates. In virtual memory systems, the

organizational issues are different. All virtual memory systems are fully associative, in that virtual memory pages may be located anywhere in main memory. The size of the main memory, which acts as a cache for the virtual memory, is generally fixed by issues which have little relation to virtual memory. Instead it is the virtual memory that is adjusted to match the amount of physical memory. Thus, for all of these reasons, it was deemed not necessary to analyze the miss rate of virtual memory, but simply the percentage of data that resides in each level.

Second, the above formula did not take into account the fact that virtual memory pages cannot be located in parallel with accessing them, as can be done with caches. Even for pages located in main memory, each virtual memory access requires at least two accesses to main memory, one to determine the location of the page, and then one to actually retrieve the page.

Third, the Patterson and Hennessy formula did not include the effect of block transfer rates. While this effect may be unimportant in analyzing caches, it can be highly significant in virtual memory systems. Hard disk drives may have terribly long access times, but they have much lower transfer times. Once data have been located on a disk, they are transferred at the speed of rotation of the disk. Competing technologies, such as flash memory, have better access times but higher transfer times than hard disk drives. To evaluate the effect of using different technologies for virtual memory, it was vital to include block transfer times in the final formula. As presented in Chapter 1, two final formulas for this model were derived:

$$A_{seq} = R_c + 2(R_m/B_c + T_m)(P_m + P_v) + (R_v/B_v + T_v)P_v$$

(1.2)

$$A_{\text{stride}} = R_{\text{c}} + 2(R_{\text{m}} + T_{\text{m}}B_{\text{m}})(P_{\text{m}} + P_{\text{v}}) + (R_{\text{v}} + T_{\text{v}}B_{\text{v}})(P_{\text{m}} + P_{\text{v}})$$

(1.3)

where

$A_{seq}$  = average time to access a byte of data from the entire hierarchy, when it is accessed sequentially

$A_{\text{stride}}$  = average time to access a byte of data from the entire hierarchy, when it is accessed in a strided manner, with the strides equal to size of a virtual memory page

$R_c$  = time to access a random byte of data in the cache (SRAM)

$R_m$  = time to access a random byte of data in the main memory (DRAM)

$R_v$  = time to access a random byte of data in the virtual memory (HDD)

$P_m$  = percentage of all unique data found in the main memory

$P_v$  = percentage of all unique data found on the disk